Quadrature Upconverter for Optical –Comms subcarrier generation

Andy Talbot G4JNT 2011-07-27

#### **Basic Design Overview**

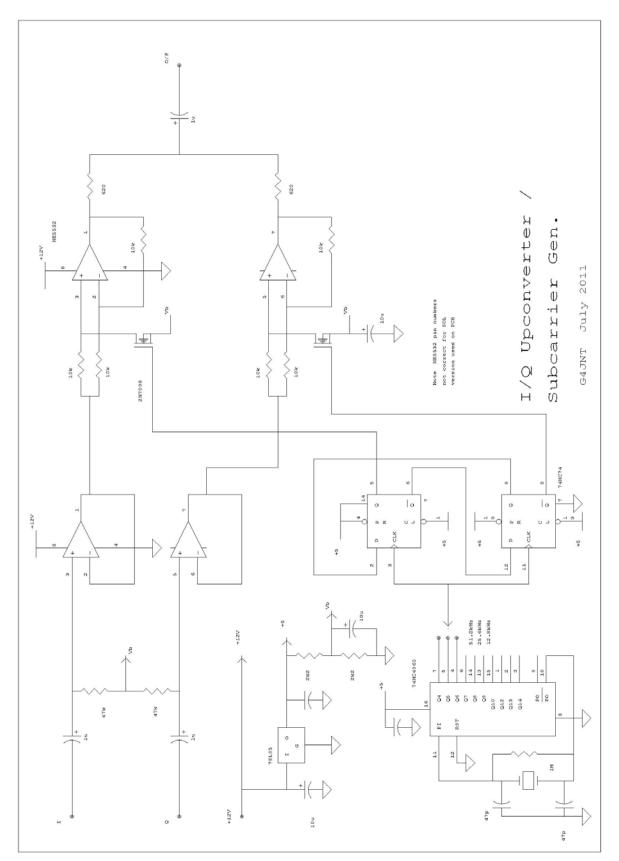

This source is designed for upconverting a baseband I/Q source such as from SDR transmitter software [1], to a subcarrier for linearly modulating an optical transmitter. The circuit is shown in Figure 1. The subcarrier is generated from a crystal oscillator and divider, the frequency is not important, and several factors of divide-by-two are link selectable, so any reasonable choice of crystal is allowed. The 3.2768MHz one here gives subcarrier frequencies of 12.8kHz, 25.6kHz or 51.2kHz. A 74HC74 dual D-type flip flop generates quadrature Local Oscillator drive signals

Baseband I and Q inputs (at audio frequencies) are buffered in a pair of unity gain opamp stages which then go to a pair of opamp single balanced mixers. When the 2N7000 FET switches are off (drive signal low) the opamps function as unity gain stages, with an output voltage exactly equal to that on the input. When the FET is switched on, the configuration changes to an inverting amplifier with gain given by the ratio of the feedback resistors. As these are equal in value, the gain is now -1. So the baseband input is multiplied by a square wave of peak value +1/-1. The output from each is now the product of the drive signal with all the odd harmonics of the carrier.

The outputs from the two mixers driven by I and Q local oscillators is summed. When the two baseband drives are a valid quadrature pair, the resulting output is an SSB upconversion with cancellation of the opposite sideband, plus a lot of spurious outputs at odd harmonics of the LO.

#### **Some Practical Issues**

Ideally, filtering needs to be added to remove the odd LO harmonics, which are at levels as high as –10dBc. But, for optical comms purposes this is probably not too important – unless there is a possibility of receiving stations inadvertently trying to listen to the higher subcarrier harmonics. (The sideband is alternately reversed for each successive odd harmonic). A simple LC filter designed for 300 ohms (defined by the two 620 ohms summing resistors) will do the job.

Carrier rejection is poor. This design of audio frequency mixer is single balanced and gives no inherent rejection of the LO signal. The leakage mechanism, in practice, is direct injection of the switching signal present on the gate of the switching FETs direct into the opamp via device junction capacitance. At maximum output, the carrier is only –15dBc, which for standard RF purposes would be completely unacceptable – but again, for optical comms purposes, is irrelevant as when receiving SSB it is tuned for zero beat.

Sideband rejection is excellent. Theoretically, the mixer would become unbalanced with unequal resistors in its feedback path and sideband rejection would suffer. In practice, using 1% resistors 50dB sideband rejection was seen straightaway.

## **Circuit Design Detail**

NE5532 opamps were used here because a) they have good high frequency performance, b) a good drive capability, c) I have a lot.

However, they do not work with their inputs particularly close to the negative rail (ground). The voltage on the input pins needs to be at least 1V above ground at all times; equivalent to bias plus maximum negative voltage excursion. To be able to run from a single polarity supply the opamps have to be biased to some intermediate voltage which is shown in Figure 1 as the voltage Vb. Normally a value of Vcc / 2 would be used for maximum signal handling, **but** the FETs need to be driven, and as the source needs to sit at Vb, the gate drive must exceed this on its positive swing by a comfortable margin.

The 2N7000 devices are logic level FETs and are guaranteed to turn on fully at 3.1V worst case. In practice the are sufficiently saturated at +2 and a bias voltage of no more than 3V will ensure this. Assuming an audio / baseband input of 2V peak-peak – the standard from most soundcards – to ensure the inputs stay at least 1V above ground, Vb has to be greater than 2V. So 2.5V is the obvious choice, and is conveniently generated by dividing down from the 5V regulated supply for the logic in the two 2.2k $\Omega$  resistors.

More complex FET drive circuitry would allow a higher value of Vb, also running the logic from 6V would be permissible with the HC family for a bit more margin, but results are OK as they are, so no further changes were made.

### Results

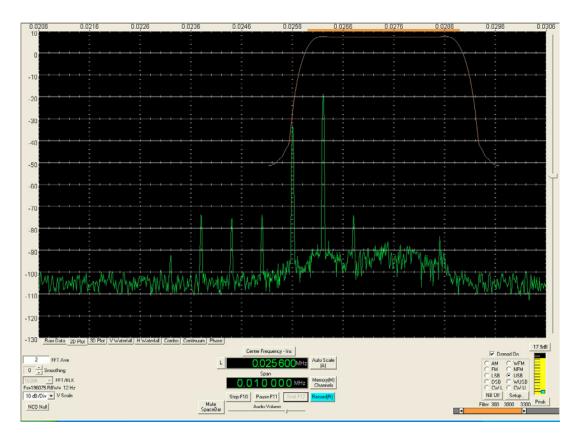

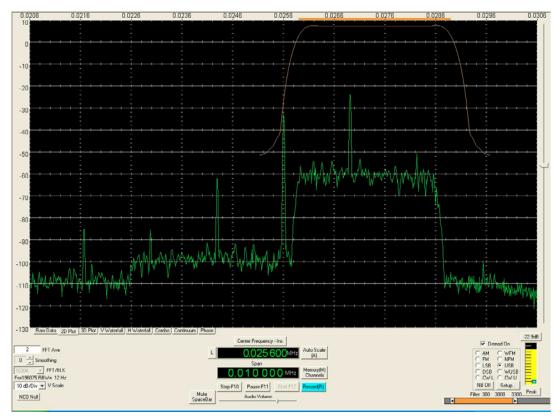

Figure 2 shows the resulting spectrum when driven by an SDR2GO [2 transmitter using its internal 600Hz CW tone. Figure 3 has the SDR2GO used in SSB mode with an audio input made up from a tone mixed with white noise. Note the poor carrier rejection of barely 15dB, but the excellent sideband rejection of >50dB in CW mode. This was achieved with no trimming. Using the amplitude and phase adjust facility on the SDR2GO module, sideband rejection of 70dB was seen at a single tone frequency!

# PCB Layout.

A PCB using SMT construction can be seen in outline Figure 4. A separate .PDF of the PCB can be found at [3]. A ground plane is on the underside connected via the 9 through holes. Note that the PCB was laid out for the rather-odd SOL wide spaced version of the NE5532 device with non-standard pin connections. I have a lot of these types, and none of the conventional ones either in DIP or SMT packages. Figure 1 shows the pin connections for these conventional packages (as my circuit drawing software does not offer the SOL option!)

| References |                          |                                         |

|------------|--------------------------|-----------------------------------------|

| [1]        | SDR Transmitter Software | http://www.g4jnt.com/SDRTxSW.htm        |

| [2]`       | SDR2GO Module            | http://www.qsl.net/k5bcq/Kits/Kits.html |

| [3]        | File                     | PCB Design_ SC_TX.pdf                   |

Figure 2 Driven from SDR2GO module in CW mode

Figure 3 Driven from SDR2GO in SSB mode, tone + white noise drive

Figure 4 PCB Outline